Phase Locked Loop که به اختصار به آن PLL گفته می شود نام مداری است که در خروجی سیگنالی متناوب تولید می کند که فاز آن مرتبط با فاز ورودی است . در صورتی که PLL در ناحیه قفل قرار بگیرد ، فاز بین ورودی و خروجی صفر می شود که در این حالت با استفاده از یک تقسیم کننده فرکانس ، PLL را به یک سینتی سایزر تبدیل نمود .

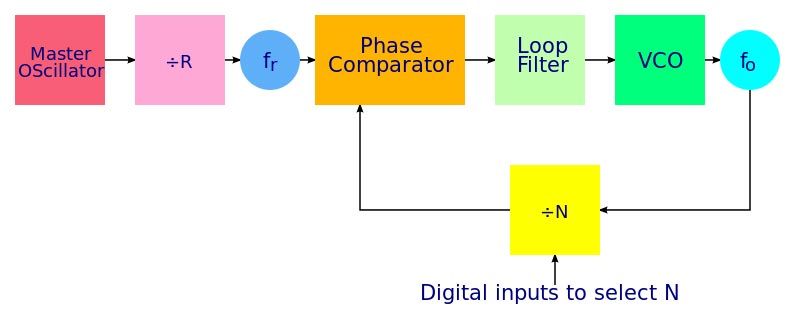

یک PLL به طور معمول از 3 بلوک اصلی آشکار ساز فاز PD ، فیلتر پایین گذر و اسیلاتور کنترل شده با ولتاژ تشکیل می شود که خروجی آن به ورودی آشکار ساز فاز فیدبک شده است . شکل زیر یک واحد PLL را نمایش می دهد که در حلقه فیدبک از یک تقسیم کننده فرکانس استفاده شده است . همچنین یک منبع فرکانس و یک تقسیم کننده نیز در ورودی PLL قرار گرفته است .

از PLL برای همزمان سازی و سنتز فرکانسی استفاده می شود . همانطور که گفته شد با قرار دادن یک واحد تقسیم کننده در حلقه فیدبک می توان فرکانس خروجی را چند برابر نمود . همچنین می توان از PLL به عنوان دمودلاتور FM و AM استفاده نمود .

کتاب پیش رو به برسی عملکرد ، شبیه سازی و طراحی واحد PLL پرداخته است .

نام انگلیسی : PLL Performance , Simulation and Design

نویسنده : Dean Banerjee